Applications of RISC-V in IoT, Grid Edge, Digital Twin, and TinyML Ecosystems

and the Role of IAS-Research.com in Accelerating Innovation

Abstract

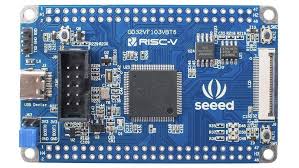

The convergence of open-source hardware, embedded systems, and machine learning is transforming digital infrastructure. The RISC-V instruction set architecture (ISA) is gaining traction in Internet of Things (IoT) devices, grid-edge computing, and Tiny Machine Learning (TinyML) applications due to its openness, efficiency, and adaptability. Complementary technologies such as SystemC, QEMU, Embedded Linux, and virtual platforms for hardware/software co-design provide powerful methods for prototyping, verification, and deployment. Coupled with digital twins, these ecosystems enable real-time monitoring, predictive analytics, and localized intelligence at the edge. This paper examines RISC-V’s role in these domains, highlights the challenges and opportunities of hardware/software co-design, and demonstrates how IAS-Research.com can provide value in accelerating innovation.

1. Introduction

The growth of IoT and smart grids demands energy-efficient, secure, and flexible computing at the network edge. Proprietary ISAs constrain innovation with licensing costs and limited customizability. By contrast, RISC-V’s royalty-free architecture enables domain-specific optimizations, particularly important in TinyML and digital twin workloads.

The success of these systems depends on hardware/software co-design—a methodology where hardware architecture and software stacks are developed in tandem. Virtual platforms such as SystemC-based simulators and QEMU emulators allow early validation of embedded software, reducing development costs and risks before silicon is manufactured.

In parallel, Embedded Linux provides a rich runtime environment for RISC-V gateways and grid-edge controllers, bridging resource-constrained nodes with cloud platforms and digital twins.

2. Applications of RISC-V in Emerging Ecosystems

2.1 IoT Devices

- Example: Low-power RISC-V MCUs running quantized ML models for precision agriculture.

- Co-Design Relevance: SystemC transaction-level models (TLM) simulate sensor interfaces, while QEMU executes firmware virtually to validate drivers and ML kernels.

2.2 Grid-Edge Computing

- Example: RISC-V edge controllers integrated with Embedded Linux for renewable energy load balancing.

- Co-Design Relevance: Hardware/software trade-offs (e.g., hardware accelerators for cryptography, software stacks for SCADA) can be evaluated in virtual platforms before deployment.

2.3 Digital Twin Systems

- Example: Substation digital twins fed by RISC-V sensor nodes for predictive maintenance.

- Co-Design Relevance: SystemC models integrate with real-time simulation environments (e.g., OPAL-RT, MATLAB/Simulink) for hardware-in-the-loop testing.

2.4 TinyML Ecosystem

- Example: RISC-V embedded boards running compressed CNNs for wildlife conservation.

- Co-Design Relevance: Virtual platforms simulate energy consumption, memory bandwidth, and ML inference latency, guiding design choices.

3. Challenges

- Performance vs. Energy: Balancing low-power requirements with real-time ML workloads.

- Simulation Fidelity: Virtual platforms must balance abstraction and cycle accuracy.

- Security & Reliability: Critical in IoT and grid-edge environments.

- Software Ecosystem: Adapting compilers, libraries, and frameworks (TensorFlow Lite Micro, TVM) to RISC-V platforms.

- Integration Complexity: Bridging RISC-V with heterogeneous devices in IoT and grid environments.

4. Opportunities Enabled by RISC-V and Virtual Platforms

- Custom ISA Extensions: Co-designed with TinyML workloads for quantized inference.

- SystemC Models: Enable hardware/software partitioning decisions early in design.

- QEMU Virtualization: Rapid firmware validation without waiting for hardware prototypes.

- Embedded Linux: Scalable runtime for grid-edge and gateway devices.

- Virtual Platforms for Digital Twins: Combine real-time data with simulated RISC-V platforms for system-level validation.

5. Hardware/Software Co-Design with Virtual Platforms

Hardware/software co-design ensures that architectural trade-offs are validated before physical silicon or large-scale deployment.

5.1 Virtual Platforms in the Workflow

- SystemC TLM Models: Used to evaluate processor cores, interconnects, and accelerators.

- QEMU Emulation: Runs unmodified RISC-V binaries, enabling OS and application validation.

- Hybrid Simulation: Combines cycle-accurate SystemC models for critical blocks with QEMU for higher-level execution.

- Embedded Linux Integration: Provides an application-ready environment for IoT and grid-edge software stacks.

5.2 Benefits

- Faster time-to-market through early validation.

- Reduced costs from fewer hardware iterations.

- Optimized performance/power trade-offs via co-simulation.

- Increased reliability through system-level testing with digital twins.

6. Role of IAS-Research.com

IAS-Research.com can provide expertise and infrastructure for end-to-end RISC-V development with co-design methodologies:

6.1 SystemC & Virtual Platform Modeling

- Create transaction-level models of RISC-V cores and accelerators.

- Integrate digital twin models for IoT and energy systems.

6.2 QEMU & Software Virtualization

- Develop RISC-V QEMU extensions for custom hardware.

- Enable embedded firmware validation and OS bring-up before silicon.

6.3 Embedded Linux & Middleware Support

- Develop board support packages (BSPs) for RISC-V SoCs.

- Optimize ML runtimes and communication protocols.

6.4 Hardware/Software Partitioning

- Identify performance-critical workloads for hardware acceleration.

- Benchmark energy and latency trade-offs in virtual platforms.

6.5 Security & Standards Compliance

- Hardened Embedded Linux configurations.

- Compliance guidance for IoT/grid standards (IEC 61850, IEEE 2030, NIST).

6.6 Collaborative Research & Training

- Partner with academia and industry to advance RISC-V adoption.

- Provide training on SystemC, QEMU, TinyML deployment, and co-design.

7. Conclusion

RISC-V provides an open and customizable ISA that is well-suited to IoT, grid-edge, TinyML, and digital twin applications. The success of these ecosystems depends on hardware/software co-design, enabled by virtual platforms such as SystemC and QEMU, along with Embedded Linux for deployment. IAS-Research.com is uniquely positioned to guide organizations in these domains by offering simulation, prototyping, optimization, and integration services. Through these capabilities, IAS-Research.com helps reduce risk, accelerate innovation, and unlock the full potential of edge intelligence.

References

- Conti, F. et al., EXTREM-EDGE: Extensions to RISC-V for Energy-Efficient ML Inference at the Edge of IoT, 2022.

- Accellera Systems Initiative, SystemC Standard Overview, 2023.

- Bellard, F., QEMU: A Generic and Open Source Machine Emulator and Virtualizer, 2022.

- Krogh, B., Embedded Linux for RISC-V SoCs: Design and Optimization, 2023.

- RISC-V International, RISC-V Processors for Edge AI Devices, 2024.

- Jagannath, A. et al., Digital Twins for Wireless Networks: Concepts and Applications, WiseML, 2022.

Applications of RISC-V in IoT, Grid Edge, Digital Twin, and TinyML Ecosystems

and the Role of IAS-Research.com in Accelerating Innovation

Abstract

The convergence of open-source hardware, embedded systems, and machine learning is reshaping digital infrastructure across industries. The RISC-V instruction set architecture (ISA) is gaining traction in Internet of Things (IoT) devices, grid-edge computing, and Tiny Machine Learning (TinyML) applications due to its modularity, efficiency, and openness. Complementary technologies such as SystemC modeling, Embedded Linux, and QEMU virtualization provide robust frameworks for simulation, software development, and system prototyping. Coupled with digital twin platforms, these ecosystems enable real-time monitoring, predictive analytics, and intelligent decision-making at the edge. This white paper explores the opportunities and challenges in deploying RISC-V in these domains and outlines how IAS-Research.com can play a pivotal role in research, design, and implementation.

1. Introduction

IoT and grid-edge infrastructures require lightweight, low-power, and secure computing platforms. Traditional proprietary ISAs often impose licensing fees and limit design flexibility. RISC-V provides a royalty-free, extensible alternative, allowing developers to tailor instruction sets for specific workloads in edge and TinyML applications.

Simulation and prototyping tools like SystemC, QEMU, and Embedded Linux accelerate RISC-V adoption. SystemC enables hardware/software co-design at the transaction level, while QEMU supports emulation of RISC-V devices, reducing hardware dependency in early development. Embedded Linux provides a flexible OS environment for higher-end RISC-V devices in IoT gateways, grid controllers, and edge servers.

Simultaneously, digital twins—virtual representations of physical systems—are increasingly used to model, simulate, and optimize grid and IoT operations. When combined with TinyML and RISC-V, they enable localized intelligence, improving resilience while reducing reliance on cloud infrastructure.

2. Applications of RISC-V in Emerging Ecosystems

2.1 IoT Devices

- Use Case: Smart agriculture sensors powered by RISC-V SoCs running TinyML for soil and crop monitoring.

- Embedded System Angle: Deployment on RISC-V microcontrollers with real-time operating systems (RTOS).

- Benefits: Energy efficiency, lightweight protocol integration, adaptability through open-source toolchains.

2.2 Grid-Edge Computing

- Use Case: Edge controllers in smart grids using RISC-V processors with Embedded Linux for predictive load balancing.

- Benefits: Real-time decision-making, integration with SCADA systems, lower latency than cloud-first solutions.

2.3 Digital Twin Systems

- Use Case: RISC-V embedded devices feed live data to digital twins of substations and renewable energy plants.

- SystemC & QEMU Role:

- SystemC models simulate how new RISC-V accelerators interact with grid protocols.

- QEMU allows virtual deployment of firmware and digital twin clients before physical rollout.

- Benefits: Accelerated testing, reduced downtime, predictive maintenance.

2.4 TinyML Ecosystem

- Use Case: Wildlife monitoring nodes running quantized ML models on RISC-V microcontrollers.

- Embedded Linux Role: Supports hybrid models where gateways run heavier inference tasks.

- Benefits: Privacy-preserving inference, minimal bandwidth requirements, extended battery life.

3. Challenges

- Resource Constraints: TinyML workloads must run within kilobytes of memory and milliwatts of power.

- Simulation Complexity: Balancing accuracy and speed in SystemC and QEMU co-simulations.

- Security & Reliability: Edge devices in critical infrastructure must resist cyber and physical attacks.

- Model Deployment: OTA (Over-the-Air) ML model updates require robust runtime integration with Embedded Linux.

- Standards Compliance: IoT and grid devices must adhere to IEEE, IEC, and NIST security standards.

4. Opportunities Enabled by RISC-V & Supporting Tools

- Custom ISA Extensions: Optimized for ML inference kernels and DSP tasks.

- SystemC Modeling: Enables hardware/software co-design of RISC-V processors and peripherals at transaction-level granularity.

- QEMU Virtualization: Offers a cost-effective way to emulate RISC-V devices, debug software, and integrate TinyML frameworks without silicon.

- Embedded Linux Integration: Provides a powerful OS environment for gateways, controllers, and higher-performance RISC-V cores.

- Scalability: From ultra-low-power MCUs to Linux-capable SoCs, enabling flexible deployment across ecosystems.

5. Role of IAS-Research.com

IAS-Research.com can act as a strategic research and engineering partner in accelerating RISC-V adoption for IoT, grid-edge, digital twins, and TinyML by leveraging embedded systems, simulation tools, and co-design expertise.

5.1 Architectural Design & Prototyping

- RISC-V ISA extensions for ML and DSP acceleration.

- SystemC models for early validation of embedded SoCs.

- FPGA-based prototyping for hardware-in-the-loop (HIL) testing.

5.2 Virtualization & Software Development

- QEMU-based emulation for firmware and OS validation.

- Embedded Linux board support package (BSP) customization for RISC-V SoCs.

- Cross-compilation toolchains for TinyML runtimes (TFLite Micro, MicroTVM).

5.3 Benchmarking & Simulation

- End-to-end evaluation of latency, energy, and ML accuracy.

- Digital twin co-simulation with SystemC + physical IoT testbeds.

5.4 Security & Standards Compliance

- Hardened Embedded Linux configurations.

- Secure boot and firmware validation workflows.

- Compliance with energy and IoT standards (IEC 61850, IEEE 2030).

5.5 End-to-End Integration

- Bridging sensor networks with RISC-V embedded nodes.

- Cloud-edge orchestration for grid and IoT ecosystems.

5.6 Research & Collaboration

- Open-source SystemC models for community use.

- Industry-academic partnerships to explore domain-specific accelerators.

6. Conclusion

RISC-V is reshaping IoT, grid-edge, TinyML, and digital twin ecosystems by enabling open, customizable, and efficient computing. SystemC, QEMU, and Embedded Linux provide the essential infrastructure for simulation, prototyping, and deployment of RISC-V-based solutions. IAS-Research.com, through its expertise in hardware/software co-design, embedded systems, simulation, and integration, is uniquely positioned to guide organizations in adopting RISC-V and realizing the full potential of edge intelligence.

References

- Conti, F. et al., EXTREM-EDGE: Extensions to RISC-V for Energy-Efficient ML Inference at the Edge of IoT, 2022.

- RISC-V International, RISC-V Processors Addressing Edge AI Devices, 2024.

- Accellera Systems Initiative, SystemC Standard Overview, 2023.

- Bellard, F., QEMU: A Generic and Open Source Machine Emulator and Virtualizer, 2022.

- Krogh, B., Embedded Linux for RISC-V SoCs: Design and Optimization, 2023.

- Jagannath, A. et al., Digital Twins for Wireless Networks: Concepts and Applications, WiseML, 2022.